# LCD MODULE SPECIFICATION

Model: CV320240D - \_ \_ - \_ - \_ - \_

| Revision      | 05            |

|---------------|---------------|

| Engineering   | LONGSON YEUNG |

| Date          | 20 AUG 12     |

| Our Reference | 4947          |

ADDRESS: 1<sup>st</sup> FLOOR, EFFICIENCY HOUSE, 35 TAI YAU STREET, SAN PO KONG,

KOWLOON, HONG KONG.

TEL : (852) 2341 3238 (SALES OFFICE) (852) 2342 8228 (GENERAL OFFICE)

FAX : (852) 2357 4237 (SALES OFFICE)

E-MAIL : cdl@cloverdisplay.com

URL : <a href="http://www.cloverdisplay.com">http://www.cloverdisplay.com</a>

### 1. MODE OF DISPLAY

Display mode **Display condition** Viewing direction STN: Yellow green Reflective type 6 O' clock Transflective type ☐ 12 O' clock Grey ☐ Blue (negative) 3 O' clock Transmissive type ☐ FSTN positive Others 9 O' clock FSTN negative

### 2. LCD MODULE NUMBER NOTATION:

| CV32024 | <u> 40D</u> - <u>MY</u> - | <u>S</u> | <u>F</u> - | <u>N</u> | <u>6</u> – | <u>T</u> |

|---------|---------------------------|----------|------------|----------|------------|----------|

|         |                           |          |            |          |            |          |

| (1)     | (2)(3)                    | (4)      | (5)        | (6)      | (7)        | (8)      |

\*(1)---Model number of standard LCD Modules

\*(2)---Backlight type

$N-No\ backlight$

E – EL backlight

L – Side-lited LED backlight

M- Array LED backlight

C-CCFL

\*(3)---Backlight color

N – No backlight

A - Amber

B - Blue

O- Orange

W-White

Y - Yellow green

\*(4)---Display mode

T - TN

V – TN (Negative)

S - STN Yellow green

G – STN Grey

B – STN Blue (Negative)

F-FSTN

N – FSTN (Negative)

\*(5)---Rear polarizer type

R – Reflective

F-Transflective

T-Transmissive

\*(6)---Temperature range

N - Normal

W-Extended

\*(7)---Viewing direction

6-6 O'clock

2 – 12 O'clock

3 - 3 O'clock

9 – 9 O'clock

\*(8)---Special code for other requirements

(Can be omitted if not used)

T – Touch panel (Analog)

P – Touch panel (Digital)

### 3. GENERAL DESCRIPTION

Display mode : 320 x 240 dots, graphic TAB LCD module

Interface : 4-bit Parallel

Driving method : 1/240 duty, 1/15 bias

Backlight : Side-lited LED

Driver IC : Integrated Solutions Technology IST3025, IST3026 or equivalence

For the detailed information, please refer to the IC specifications.

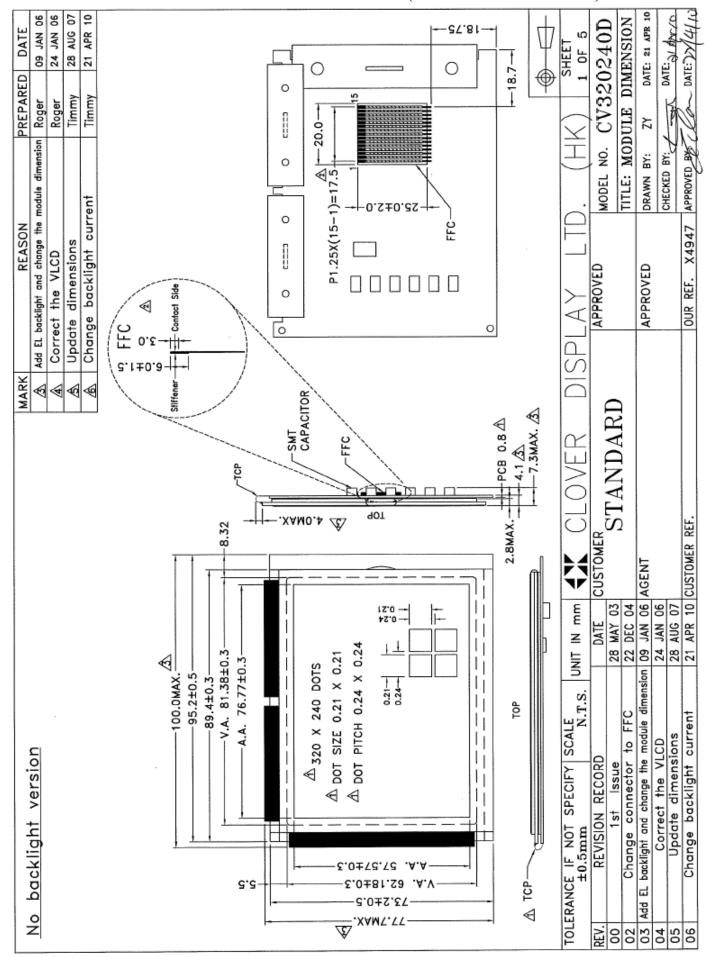

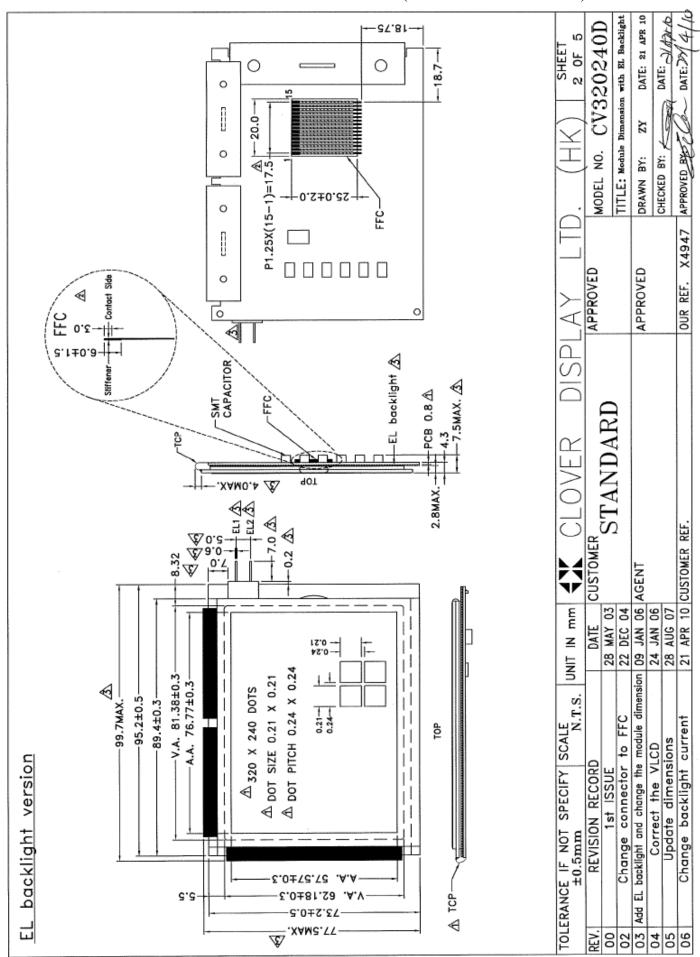

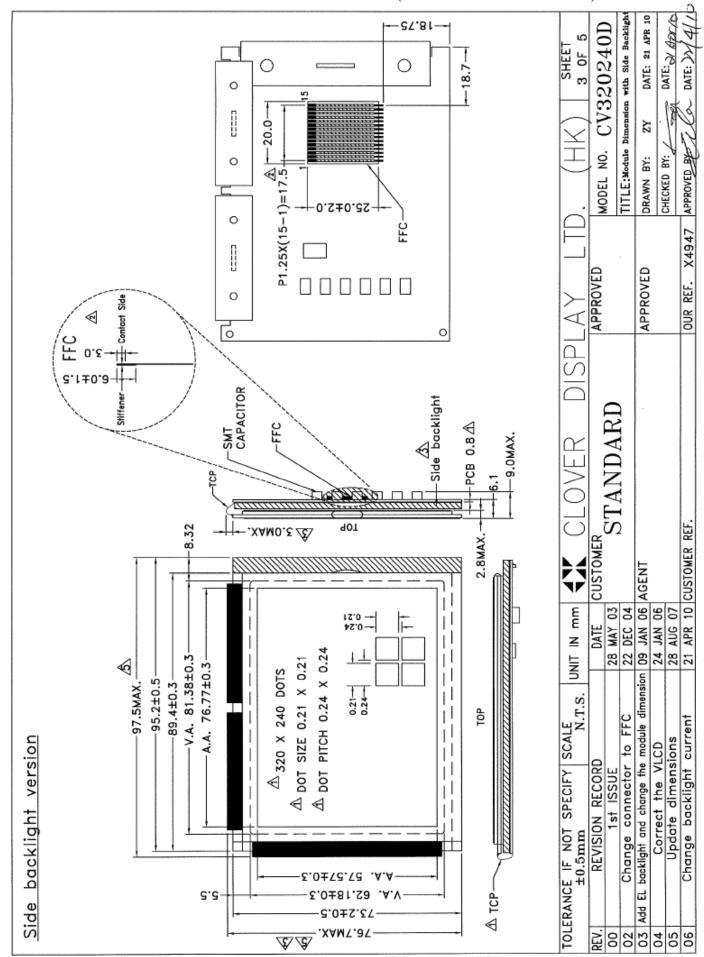

## 4. MECHANICAL DIMENSIONS

| Item               | Dimension               | Unit | Item         | Dimension         | Unit |

|--------------------|-------------------------|------|--------------|-------------------|------|

| Outline Dimension  |                         |      |              |                   |      |

| No Backlight (N)   | 100(L)x77.7(W)x7.5(H)   | mm   | Dot Pitch    | 0.24(L)x0.24(W)   | mm   |

| Side Backlight (L) | 97.5(L)x76.7(W)x9.05(H) | mm   | Viewing Area | 81.38(L)x62.18(W) | mm   |

| EL Backlight (E)   | 99.7(L)x77.5(W)x7.5(H)  | mm   | Dot Size     | 0.21(L)x0.21(W)   | mm   |

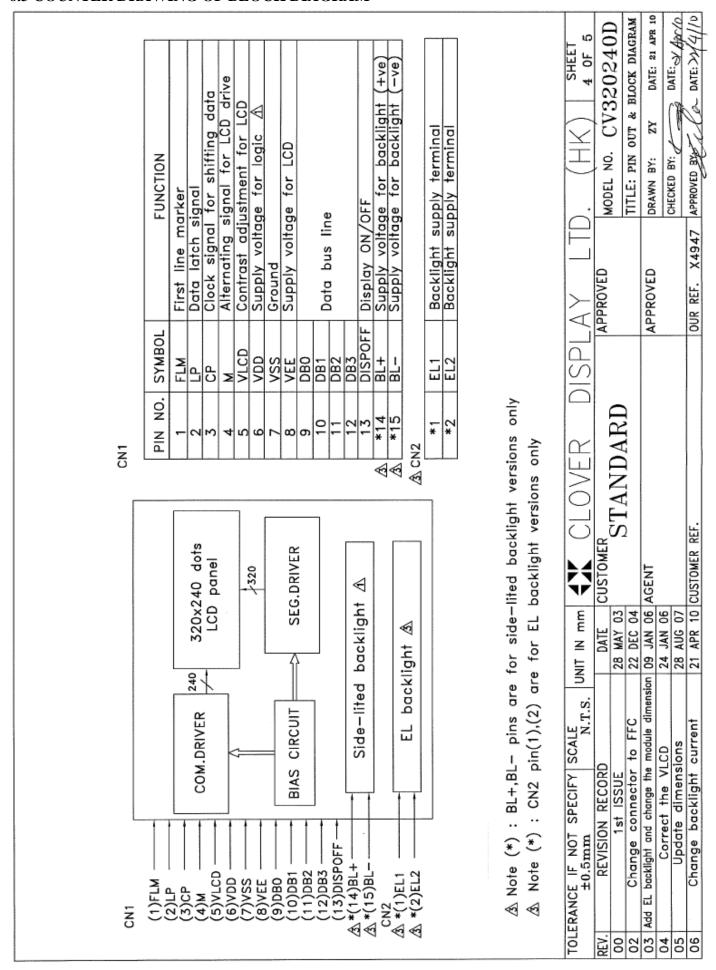

### 5. CONNECTOR PIN ASSIGNMENT

| Pin No. | Symbol | Function                       | Pin No. | Symbol  | Function                         |

|---------|--------|--------------------------------|---------|---------|----------------------------------|

| 1       | FLM    | First Line Marker              | 9       | DB0     |                                  |

| 2       | LP     | Data latch signal              | 10      | DB1     | Data Bus Line                    |

| 3       | СР     | Clock signal for shifting data | 11      | DB2     |                                  |

| 4       | M      | Alternate signal for LCD drive | 12      | DB3     |                                  |

| 5       | VO     | Contrast Adjustment for LCD    | 13      | DISPOFF | Display On/Off                   |

| 6       | VDD    | Supply Voltage for Logic       | 14      | BL+     | Supply voltage for backlight(+)  |

| 7       | Vss    | Ground                         | 15      | BL-     | Supply voltage for backlight (-) |

| 8       | VEE    | Power supply for LCD           | _       | _       | _                                |

## **CN 2**

| Pin No. | Symbol | Function                  |

|---------|--------|---------------------------|

| 1       | EL1    | Backlight supply terminal |

| 2       | EL2    | Backlight supply terminal |

SPEC. REV.05 PAGE 2 OF 15

### 6. COUNTER DRAWING OF MODULE DIMENSION (WITHOUT BACKLIGHT)

### 6.1 COUNTER DRAWING OF MODULE DIMENSION (WITH EL BACKLIGHT)

### 6.2 COUNTER DRAWING OF MODULE DIMENSION (WITH SIDE BACKLIGHT)

### 6.3 COUNTER DRAWING OF BLOCK DIAGRAM

CV320240D

# 7. ELECTRICAL CHARACTERISTICS

| Item                    | Symbol | MIN.   | TYP. | MAX.    | Unit |

|-------------------------|--------|--------|------|---------|------|

| Supply Voltage          | VDD    | 4.5    | 5.0  | 5.5     | V    |

| Supply Current          | IDD    | _      | 0.19 | 0.29    | mA   |

| Power supply for LCD    | VEE    | 25.0   | _    | 30.0    | V    |

| "H"Level Input Voltage  | VIH    | 0.8VDD |      | VDD     | V    |

| "L"Level Input Voltage  | VIL    | 0      | _    | 0.2 VDD | V    |

| LCD Contrast Adjustment | V0     | 22.8   | 24.0 | 25.2    | V    |

## Side Backlight:

Constant voltage driving:

| Item                    | Symbol            | MIN. | TYP. | MAX. | Unit | Condition       |

|-------------------------|-------------------|------|------|------|------|-----------------|

| White Backlight current | $I_{\mathrm{BL}}$ | _    | 102  | 108  | mA   | $V_{BL} = 3.6V$ |

| Blue Backlight current  | $I_{\mathrm{BL}}$ | _    | 102  | 108  | mA   | $V_{BL} = 3.6V$ |

## EL Backlight:

| Item              | Symbol   | MIN. | TYP. | MAX. | Unit | Condition        |

|-------------------|----------|------|------|------|------|------------------|

| Backlight Voltage | $V_{EL}$ |      | 100  | 150  | Vrms | Frequency= 400Hz |

## 7.1. ABSOLUTE MAXIMUM RATINGS

Please make sure not to exceed the following maximum rating values under the worst application conditions

| Item                  | Symbol | Rating (for normal temperature) | Rating (for wide temperature) | Unit                                                                               |

|-----------------------|--------|---------------------------------|-------------------------------|------------------------------------------------------------------------------------|

| Supply Voltage        | Vdd    | -0.3 to 7.0                     | -0.3 to 7.0                   | V                                                                                  |

| Input Voltage         | VT     | -0.3 to VDD +0.3                | -0.3 to VDD +0.3              | V                                                                                  |

| Operating Temperature | Topr   | 0 to 50                         | -20 to 70                     | $^{\circ}\!\mathbb{C}$                                                             |

| Storage Temperature   | Tstg   | -10 to 60                       | -30 to 80                     | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

SPEC. REV.05 PAGE 7 OF 15

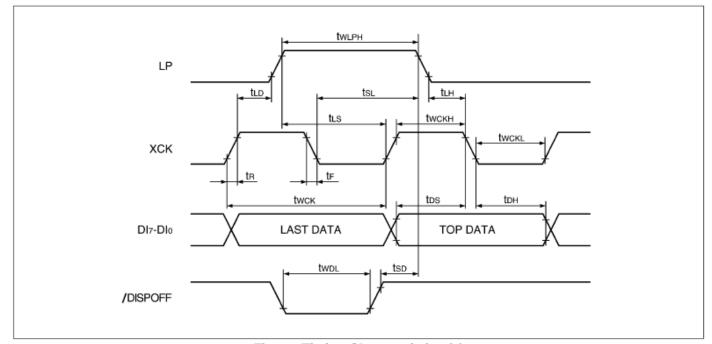

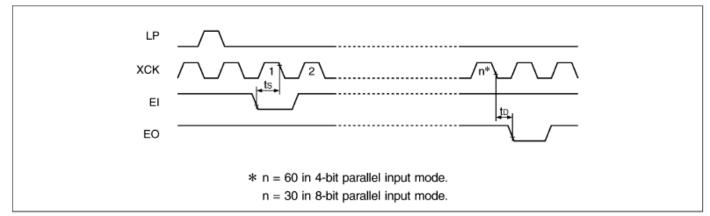

## 8. TIMING CHART OF SEGMENT MODE

Fig. 6 Timing Characteristics (1)

Fig. 7 Timing Characteristics (2)

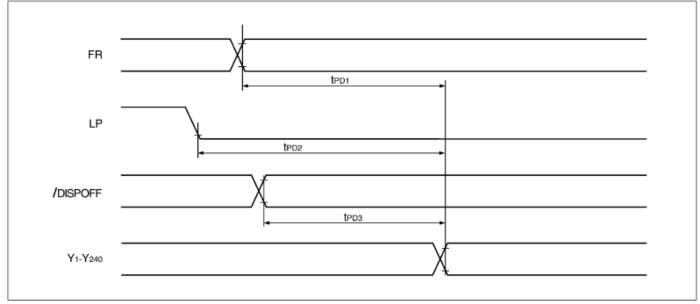

Fig. 8 Timing Characteristics (3)

SPEC. REV.05 PAGE 8 OF 15

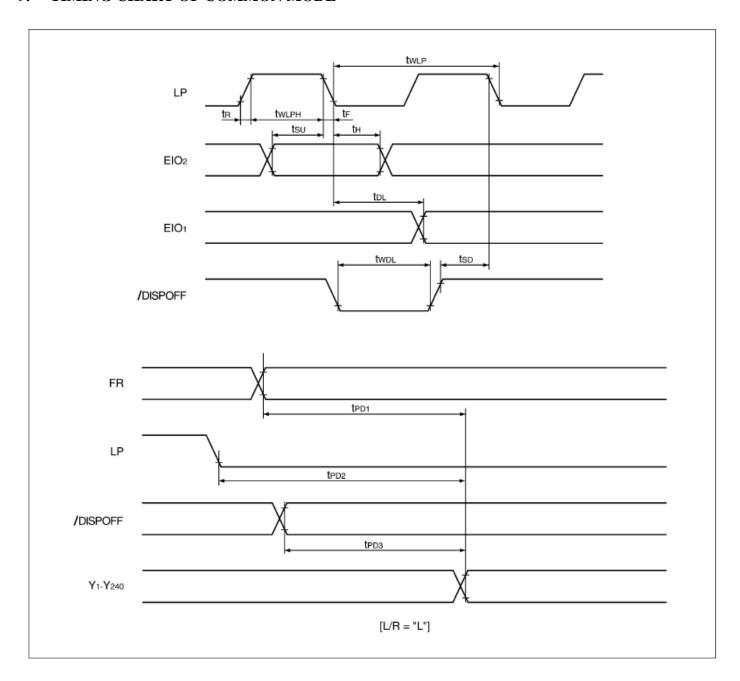

# 9. TIMING CHART OF COMMON MODE

SPEC. REV.05 PAGE 9 OF 15

# 10. AC CHARACTERISTICS

(Segment Mode 1) (V<sub>SS</sub> = V<sub>5</sub> = 0 V, V<sub>DD</sub> = +5.0  $\pm$  0.5 V, V<sub>0</sub> = +15.0 to +40.0 V, T<sub>OPR</sub> = -30 to +85  $^{\circ}$ C)

| PARAMETER                                 | SYMBOL                              | CONDITIONS                              | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|-------------------------------------|-----------------------------------------|------|------|------|------|------|

| Shift clock period                        | t <sub>wck</sub>                    | t <sub>R</sub> , t <sub>F</sub> ≤ 10 ns | 50   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | t <sub>wcĸн</sub>                   |                                         | 15   |      |      | ns   |      |

| Shift clock "L" pulse width               | t <sub>WCKL</sub>                   |                                         | 15   |      |      | ns   |      |

| Data setup time                           | t <sub>DS</sub>                     |                                         | 10   |      |      | ns   |      |

| Data hold time                            | t <sub>DH</sub>                     |                                         | 12   |      |      | ns   |      |

| Latch pulse "H" pulse width               | t <sub>WLPH</sub>                   |                                         | 15   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | t <sub>LD</sub>                     |                                         | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | t <sub>SL</sub>                     |                                         | 30   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | <b>t</b> Ls                         |                                         | 25   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | t <sub>LH</sub>                     |                                         | 25   |      |      | ns   |      |

| Enable setup time                         | ts                                  |                                         | 10   |      |      | ns   |      |

| Input signal rise time                    | t <sub>R</sub>                      |                                         |      |      | 50   | ns   | 2    |

| Input signal fall time                    | t <sub>F</sub>                      |                                         |      |      | 50   | ns   | 2    |

| /DISPOFF removal time                     | t <sub>SD</sub>                     |                                         | 100  |      |      | ns   |      |

| /DISPOFF "L" pulse width                  | t <sub>WDL</sub>                    |                                         | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | t <sub>D</sub>                      | C <sub>L</sub> = 15 pF                  |      |      | 30   | ns   |      |

| Output delay time (2)                     | t <sub>PD1</sub> , t <sub>PD2</sub> | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | t <sub>PD3</sub>                    | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

## NOTES:

- 1. Takes the cascade connection into consideration.

- 2.  $(t_{\text{WCK}^-} t_{\text{WCKH}^-} t_{\text{WCKL}})/2$  is maximum in the case of high speed operation.

SPEC. REV.05 PAGE 10 OF 15

(Segment Mode 2) (V<sub>SS</sub> = V<sub>5</sub> = 0 V, V<sub>DD</sub> = +3.0 to +4.5 V, V<sub>0</sub> = +15.0 to +40.0 V, T<sub>OPR</sub> = -30 to +85  $^{\circ}$ C)

| PARAMETER                                 | SYMBOL                              | CONDITIONS                              | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|-------------------------------------|-----------------------------------------|------|------|------|------|------|

| Shift clock period                        | twck                                | t <sub>R</sub> , t <sub>F</sub> ≤ 10 ns | 66   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twckh                               |                                         | 23   |      |      | ns   |      |

| Shift clock "L" pulse width               | t <sub>WCKL</sub>                   |                                         | 23   |      |      | ns   |      |

| Data setup time                           | t <sub>DS</sub>                     |                                         | 15   |      |      | ns   |      |

| Data hold time                            | t <sub>DH</sub>                     |                                         | 23   |      |      | ns   |      |

| Latch pulse "H" pulse width               | t <sub>WLPH</sub>                   |                                         | 30   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | t <sub>LD</sub>                     |                                         | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | t <sub>SL</sub>                     |                                         | 50   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | <b>t</b> Ls                         |                                         | 30   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | t <sub>LH</sub>                     |                                         | 30   |      |      | ns   |      |

| Enable setup time                         | ts                                  |                                         | 15   |      |      | ns   |      |

| Input signal rise time                    | t <sub>R</sub>                      |                                         |      |      | 50   | ns   | 2    |

| Input signal fall time                    | t <sub>F</sub>                      |                                         |      |      | 50   | ns   | 2    |

| /DISPOFF removal time                     | t <sub>SD</sub>                     |                                         | 100  |      |      | ns   |      |

| /DISPOFF "L" pulse width                  | t <sub>WDL</sub>                    |                                         | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | t <sub>D</sub>                      | C <sub>L</sub> = 15 pF                  |      |      | 41   | ns   |      |

| Output delay time (2)                     | t <sub>PD1</sub> , t <sub>PD2</sub> | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | t <sub>PD3</sub>                    | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

# NOTES:

- 3. Takes the cascade connection into consideration.

- 4.  $(t_{\text{WCK}^-} t_{\text{WCKH}^-} t_{\text{WCKL}})/2$  is maximum in the case of high speed operation.

SPEC. REV.05 PAGE 11 OF 15

(Segment Mode 3) (V<sub>SS</sub> = V<sub>5</sub> = 0 V, V<sub>DD</sub> = +2.5 to +3.0 V, V<sub>0</sub> = +15.0 to +40.0 V, T<sub>OPR</sub> = -30 to +85  $^{\circ}$ C)

| PARAMETER                                 | SYMBOL                              | CONDITIONS                              | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|-------------------------------------|-----------------------------------------|------|------|------|------|------|

| Shift clock period                        | t <sub>wck</sub>                    | t <sub>R</sub> , t <sub>F</sub> ≤ 10 ns | 82   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | t <sub>wckh</sub>                   |                                         | 28   |      |      | ns   |      |

| Shift clock "L" pulse width               | t <sub>WCKL</sub>                   |                                         | 28   |      |      | ns   |      |

| Data setup time                           | t <sub>DS</sub>                     |                                         | 20   |      |      | ns   |      |

| Data hold time                            | t <sub>DH</sub>                     |                                         | 23   |      |      | ns   |      |

| Latch pulse "H" pulse width               | t <sub>WLPH</sub>                   |                                         | 30   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | t <sub>LD</sub>                     |                                         | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | t <sub>SL</sub>                     |                                         | 65   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | t <sub>LS</sub>                     |                                         | 30   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | t <sub>LH</sub>                     |                                         | 30   |      |      | ns   |      |

| Enable setup time                         | ts                                  |                                         | 15   |      |      | ns   |      |

| Input signal rise time                    | t <sub>R</sub>                      |                                         |      |      | 50   | ns   | 2    |

| Input signal fall time                    | t <sub>F</sub>                      |                                         |      |      | 50   | ns   | 2    |

| /DISPOFF removal time                     | t <sub>SD</sub>                     |                                         | 100  |      |      | ns   |      |

| /DISPOFF "L" pulse width                  | t <sub>WDL</sub>                    |                                         | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | t <sub>D</sub>                      | C <sub>L</sub> = 15 pF                  |      |      | 57   | ns   |      |

| Output delay time (2)                     | t <sub>PD1</sub> , t <sub>PD2</sub> | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | t <sub>PD3</sub>                    | C <sub>L</sub> = 15 pF                  |      |      | 1.2  | μs   |      |

### NOTES:

- 5. Takes the cascade connection into consideration.

- 6.  $(t_{WCK^-} t_{WCKH^-} t_{WCKL})/2$  is maximum in the case of high speed operation.

SPEC. REV.05 PAGE 12 OF 15

## 11. ELECTRO-OPTICAL CHARACTERISTICS

MEASURING CONDITION: POWER SUPPLY =  $V_{OP}$  / 64 Hz TEMPERATURE = 23  $\pm$  5 °C

RELATIVE HUMIDITY =  $60 \pm 20 \%$

| ITEM                      | SYMBOL | UNIT | TYP. |

|---------------------------|--------|------|------|

| RESPONSE TIME             | Ton    | ms   | 370  |

|                           | Toff   | ms   | 470  |

| CONTRAST RATIO            | Cr     | -    | 7    |

|                           | V3:00  | 0    | 40   |

| VIEWING ANGLE (6 O'clock) | V6:00  | ٥    | 50   |

| (Cr ≥ 2)                  | V9:00  | ٥    | 40   |

|                           | V12:00 | ٥    | 30   |

THE ELECTRO-OPTICAL CHARACTERISTICS ARE MEASURED VALUE BUT NOT GUARANTEED ONES.

# 12. RELIABILITY OF LCD MODULE

| 12. RELIABILITY OF ECD MODULE |                               |                               |           |  |  |  |  |

|-------------------------------|-------------------------------|-------------------------------|-----------|--|--|--|--|

|                               | TEST CONDITION                | TEST CONDITION                |           |  |  |  |  |

| ITEM                          | FOR NORMAL TEMPERATURE        | FOR WIDE TEMPERATURE          | TIME      |  |  |  |  |

| High temperature operating    | 50°C                          | 70°C                          | 240 hours |  |  |  |  |

| Low temperature operating     | 0°C                           | -20°C                         | 240 hours |  |  |  |  |

| High temperature storage      | 60°C                          | 80°C                          | 240 hours |  |  |  |  |

| Low temperature storage       | -10°C                         | -30°C                         | 240 hours |  |  |  |  |

| Temperature-humidity storage  | 40°C 90% R.H.                 | 60°C 90% R.H.                 | 96 hours  |  |  |  |  |

| Temperature cycling           | -10°C to 60°C                 | -30°C to 80°C                 | 5 cycles  |  |  |  |  |

|                               | 30 Min Dwell                  | 30 Min Dwell                  |           |  |  |  |  |

| Vibration Test at LCM Level   | Freq 10-55 Hz                 | Freq 10-55 Hz                 |           |  |  |  |  |

|                               | Sweep rate: 10-55-10 at 1 min | Sweep rate: 10-55-10 at 1 min |           |  |  |  |  |

|                               | Sweep mode Linear             | Sweep mode Linear             | _         |  |  |  |  |

|                               | Displacement: 2 mm p-p        | Displacement: 2 mm p-p        |           |  |  |  |  |

|                               | 1 Hour each for X, Y, Z       | 1 Hour each for X, Y, Z       |           |  |  |  |  |

SPEC. REV.05 PAGE 13 OF 15

# 13. QUALITY STANDARD OF LCD MODULE

| 1.0 | Sampling Method                         |                  |                                     |  |  |  |  |

|-----|-----------------------------------------|------------------|-------------------------------------|--|--|--|--|

|     | Sampling Plan : MIL STD 105 E           |                  |                                     |  |  |  |  |

|     | Class of AQL : Level II/Single Sampling |                  |                                     |  |  |  |  |

|     | Critical: 0.25% Major 0.65% Minor 1.5%  |                  |                                     |  |  |  |  |

| 2.0 | Defect Group                            | Failure Category | Failure Reasons                     |  |  |  |  |

|     | Critical Defect                         | Malfunction      | Open                                |  |  |  |  |

|     | 0.25%(AQL)                              |                  | Short                               |  |  |  |  |

|     |                                         |                  | Burnt or dead component             |  |  |  |  |

|     |                                         |                  | Missing part/improper part P.C.B.   |  |  |  |  |

|     |                                         |                  | Broken                              |  |  |  |  |

|     | Major Defect                            | Poor Insulation  | Potential short                     |  |  |  |  |

|     | 0.65%(AQL)                              |                  | High current                        |  |  |  |  |

|     |                                         |                  | Component damage or scratched       |  |  |  |  |

|     |                                         |                  | or Lying too close improper coating |  |  |  |  |

|     |                                         | Poor Conduction  | Damage joint                        |  |  |  |  |

|     |                                         |                  | Wrong polarity                      |  |  |  |  |

|     |                                         |                  | Wrong spec. part                    |  |  |  |  |

|     |                                         |                  | Uneven/intermittent contact         |  |  |  |  |

|     |                                         |                  | Loose part                          |  |  |  |  |

|     |                                         |                  | Copper peeling                      |  |  |  |  |

|     |                                         |                  | Rust or corrosion or dirt's         |  |  |  |  |

|     | Minor Defect                            | Cosmetic Defect  | Minor scratch                       |  |  |  |  |

|     | 1.5%(AQL)                               |                  | Flux residue                        |  |  |  |  |

|     |                                         |                  | Thin solder                         |  |  |  |  |

|     |                                         |                  | Poor plating                        |  |  |  |  |

|     |                                         |                  | Poor marking                        |  |  |  |  |

|     |                                         |                  | Crack solder                        |  |  |  |  |

|     |                                         |                  | Poor bending                        |  |  |  |  |

|     |                                         |                  | Poor packing                        |  |  |  |  |

|     |                                         |                  | Wrong size                          |  |  |  |  |

SPEC. REV.05 PAGE 14 OF 15

#### HANDLING PRECAUTIONS

#### (1) CAUTION OF LCD HANDLING & CLEANING

The polarizing plate on the surface of the panel is made from organic substances. Be very careful for chemicals not to touch the plate or it leads the polarizing plate to deteriorate.

If the use of a chemical is unavoidable, wipe the panel lightly with soft materials, such as gauze and absorbent cotton, soaked in a solvent.

\*Usable solvent: Alcohol (ethanol, IPA and the like)

Avoid wiping with a dry cloth, since it could damage the surface of the polarizing plate and others.

### (2) CAUTION AGAINST STATIC CHARGE

The LCD modules use CMOS LSI drivers, so customers are recommended that any unused input terminal would be connected to  $V_{DD}$  or  $V_{SS}$ , do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity.

### (3) PACKAGING

Avoid intense shock and falls from a height and do not operate or store them exposed to direct sunshine or high temperature/humidity for long periods.

#### (4) CAUTION FOR OPERATION

The viewing angle can be adjusted by varying the LCD driving voltage V0.

Driving voltage should be kept within specified range, excess voltage shortens display life.

Response time increases with decrease in temperature.

Display may turn black or dark Blue at temperature above its operational range; this is however not destructive and the display will return to normal once the temperature falls back to range.

Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured". They will recover once the display is turned off.

Condensation at terminals will cause malfunction and possible electrochemical reaction. Relative humidity of the environment should therefore be kept below 60%.

## (5) SAFETY

Liquid crystal may leak out of a damaged LCD, it is recommended to wash off the liquid crystal by using solvents such as acetone or ethanol and should be burned up later.

If any liquid leak out of a damaged glass cell comes in contact with your hands, wash it off with soap and water immediately.

### **WARRANTY**

CLOVER will replace or repair any of her LCD module in accordance with her LCD specification for a period of one year from date of shipment. The warranty liability of Clover is limited to repair and/or replacement. Clover will not be responsible for any subsequent or consequential event.

SPEC. REV.05 PAGE 15 OF 15

<sup>\*</sup>Appropriate solvent: Ketones, ethyl alcohol