# LCD MODULE SPECIFICATION

Model: CV240160C - \_ \_ - \_ - \_ - \_

| Revision      | 02               |

|---------------|------------------|

| Engineering   | Jackson Fung     |

| Date          | 18 February 2016 |

| Our Reference | 4940             |

ADDRESS: 1st FLOOR, EFFICIENCY HOUSE, 35 TAI YAU STREET, SAN PO KONG,

KOWLOON, HONG KONG.

TEL : (852) 2341 3238 (SALES OFFICE) (852) 2342 8228 (GENERAL OFFICE)

FAX : (852) 2357 4237 (SALES OFFICE)

E-MAIL : <u>cdl@cloverdisplay.com</u>

URL : <a href="http://www.cloverdisplay.com">http://www.cloverdisplay.com</a>

# **MODE OF DISPLAY**

| Display mode  STN:  Yellow green  Grey  Blue (negative)  FSTN positive  FSTN negative | ☐ Refle | condition ective type sflective type smissive type ers | Viewing direction  ☐ 6 O' clock ☐ 12 O' clock ☐ 3 O' clock ☐ 9 O' clock                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------|---------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD MODULE NUMBER NO                                                                  | TATION: |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CV240160C- MY - S F - N                                                               |         | *(2)Backlight  I  I  I  I  I  I  I  I  I  I  I  I  I   | N – No backlight E – EL backlight L – Side-lited LED backlight M – Array LED backlight M – Array LED backlight C – CCFL t color N – No backlight A – Amber B – Blue D – Orange W – White Y – Yellow green mode T – TN V – TN (Negative) B – STN Yellow green G – STN Grey B – STN Blue (Negative) F – FSTN N – FSTN (Negative) arizer type R – Reflective F – Transflective T – Transmissive ture range N – Normal W – Extended |

SPEC. REV.02 PAGE 1 OF 24

### **GENERAL DESCRIPTION**

Display mode : 240 x 160 dots, graphic TAB LCD module

Interface : 4 bit / 8 bit parallel

Driving method : 1/160 duty, 1/13 bias

Backlight : Side-lited LED

Controller IC : RAIO RA8822 or equivalent

For the detailed information, please refer to the IC specifications.

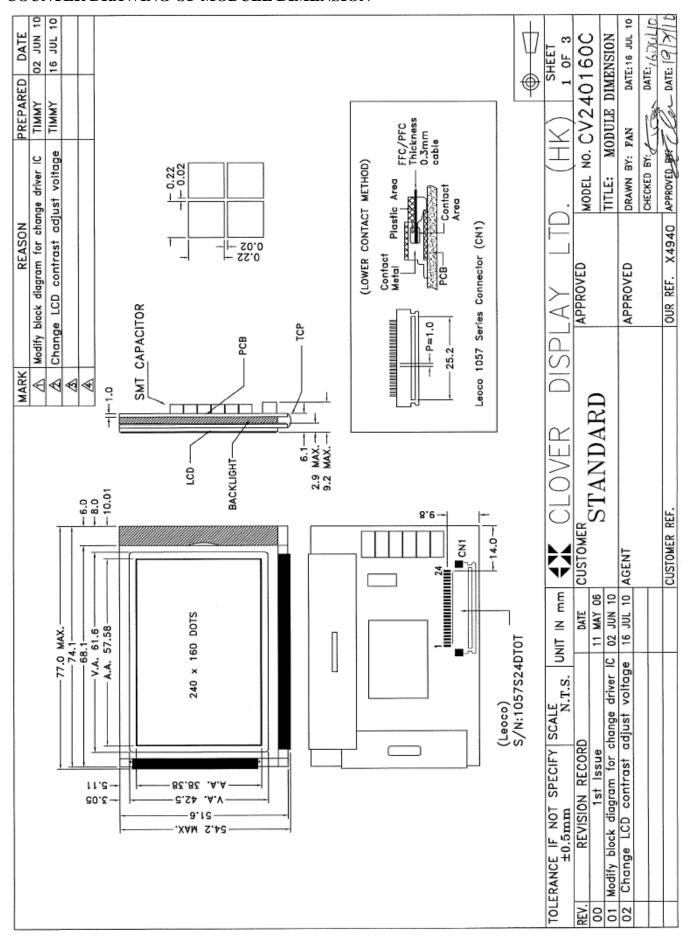

### **MECHANICAL DIMENSIONS**

| Item              | Dimension                                 | Unit |

|-------------------|-------------------------------------------|------|

| Outline Dimension | 77.0 MAX.(L) x 54.2 MAX.(W) x 9.2 MAX.(H) | mm   |

| Viewing Area      | 61.6(L)x42.5(W)                           | mm   |

| Dot Pitch         | 0.24(L)x0.24(W)                           | mm   |

| Dot Size          | 0.22(L)x0.22(W)                           | mm   |

#### CONNECTOR PIN ASSIGNMENT

| COMME   | CIONI  | III ABBIUINIENI             |         |        |                                    |

|---------|--------|-----------------------------|---------|--------|------------------------------------|

| Pin No. | Symbol | Function                    | Pin No. | Symbol | Function                           |

| 1       | RS     | Register select             | 13      | DB4    |                                    |

| 2       | WR     | Write signal                | 14      | DB5    | Data bus                           |

| 3       | RD     | Read signal                 | 15      | DB6    | Data bus                           |

| 4       | CS1    | Chip enable                 | 16      | DB7    |                                    |

| 5       | VLCD   | Contrast adjustment for LCD | 17      | CS2    | Chip enable                        |

| 6       | VDD    | Supply voltage for logic    | 18      | BSY    | Busy signal                        |

| 7       | VSS    | Ground                      | 19      | INT    | Interrupt signal                   |

| 8       | VEE    | Supply voltage for LCD      | 20      | RST    | Reset                              |

| 9       | DB0    |                             | 21      | BL+    | Supply voltage for backlight       |

| 10      | DB1    | Data bus                    | 22      | BL-    | Supply voltage for backlight (-VE) |

| 11      | DB2    | Data ous                    | 23      | NC     | No connection                      |

| 12      | DB3    |                             | 24      | NC     | No connection                      |

|         |        |                             |         |        |                                    |

SPEC. REV.02 PAGE 2 OF 24

#### COUNTER DRAWING OF MODULE DIMENSION

# COUNTER DRAWING OF PIN OUT & BLOCK DIAGRAM

|                             | (+VE)<br>(-VE)                                                                                                                                                                                                                                                                                                                                                                                     | (HK) SHEET                                             | MODEL NO. CV240160C<br>TITLE: PIN OUT & BLOCK DIAGRAM                                                            | DRAWN BY: FAN DATE: 16 JUL 10<br>CHECKED BY: A DATE: 16 JUL 10 | APPROVED BY CONDATE: 19/7/10 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------|

| CN1 PIN NO. SYMBOL FUNCTION | 1 RS Register select 2 WR Write signal 3 RD Read signal 4 CS1 Chip enable 5 V0 Contrast adjustment for LC 6 VDD Supply voltage for logic 7 VSS Ground 10 DB1 11 DB2 12 DB3 14 DB5 15 DB6 16 DB0 17 CS2 Chip enable 18 BSY Busy signal 19 BSY Busy signal 19 RST Reset 20 RST Reset 21 BL+ Supply voltage for backlight 22 BL- Supply voltage for backlight 23 NC No connection 24 NC No connection | DISPLAY LTD                                            | APPROVED                                                                                                         | APPROVED DRAW                                                  | OUR REF. X4940 APPRO         |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                    | ERANCE IF NOT SPECIFY SCALE  ±0.5mm  N.T.S. UNIT IN mm | REV. REVISION RECORD DAILE CUSTOMER OF 11 MAY 06 STANDARD OF Modify block diagram for change driver IC 02 JUN 10 | Change LCD contrast adjust voltage 16 JUL 1                    | CUSTOMER REF.                |

Conditions: VSS=0V, Ta=25°C

#### **ELECTRICAL CHARACTERISTICS**

| Item                        | Symbo | MIN. | TYP. | MAX. | Unit | Item                   | Symbol | MIN.   | TYP. | MAX.   | Unit |

|-----------------------------|-------|------|------|------|------|------------------------|--------|--------|------|--------|------|

|                             | 1     |      |      |      |      |                        |        |        |      |        |      |

| Supply Voltage for Logic    | VDD   | 4.75 | 5.0  | 5.25 | V    | Power supply for LCD   | VEE    | 21.0   | _    | 25.0   | V    |

| Supply Current for Logic    | IDD   | _    | 8.0  | 12.0 | mA   | "H"Level Input Voltage | VIH    | 0.8VDD | _    | VDD    | V    |

| LCD Contrast Adjustment (*) | VO    | 17.7 | 18.6 | 19.5 | V    | "L"Level Input Voltage | VIL    | VSS    | _    | 0.2VDD | V    |

Note (\*): There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

### **Side Backlight**

Constant current driving:

| Item              | Symbol | MIN. | TYP. | MAX. | Unit | Condition  |

|-------------------|--------|------|------|------|------|------------|

| Backlight Voltage | VBL    | 3.8  | 4.0  | 4.2  | V    | IBL = 60mA |

### **ABSOLUTE MAXIMUM RATINGS**

Please make sure not to exceed the following maximum rating values under the worst application conditions

| rease make sure not to exceed the following maximum rating values under the worst appreciation conditions |        |                                 |                                                        |                        |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------|---------------------------------|--------------------------------------------------------|------------------------|--|--|--|

| Item                                                                                                      | Symbol | Rating (for normal temperature) | (for normal temperature) Rating (for wide temperature) |                        |  |  |  |

| Supply Voltage                                                                                            | VDD    | -0.3 to 6.5                     | -0.3 to 6.5                                            | V                      |  |  |  |

| Input Voltage                                                                                             | VIN    | -0.3 to VDD +0.3                | -0.3 to VDD +0.3                                       | V                      |  |  |  |

| Operating Temperature                                                                                     | Topr   | 0 to 50                         | -20 to 70                                              | $^{\circ}\!\mathbb{C}$ |  |  |  |

| Storage Temperature                                                                                       | Tstg   | -10 to 60                       | -30 to 80                                              | $^{\circ}\!\mathbb{C}$ |  |  |  |

SPEC. REV.02 PAGE 5 OF 24

# REGISTER LIST TABLE

| Reg. | Reg. | R/W | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   | Default |

|------|------|-----|------|------|------|------|------|------|------|------|---------|

| No   | Name |     |      |      |      |      |      |      |      |      | Data    |

| 00h  | WLCR | R/W | PW1  | PW0  | SR   |      | CG   | DP   | DK   | DV   | C9h     |

| 01h  | MISC | R/W |      | CKN  |      | PLR  |      |      | CKB1 | CKB0 | F0h     |

| 02h  | APSR | R/W |      |      | SP1  | SP0  | OAR  |      | SRFS |      | 10h     |

| 03h  | ADSR | R/W |      |      |      |      | DADR | AUCM | AUSG | SGCM | 80h     |

| 10h  | WCCR | R/W | ARI  | ALG  | WDI  | WBC  | AWI  | CP   | CK   | CSD  | 6Fh     |

| 11h  | DWLR | R/W | CR3  | CR2  | CR1  | CR0  | DY3  | DY2  | DY1  | DY0  | 22h     |

| 12h  | MAMR | R/W | GIM  | RM2  | RM1  | RM0  | OP1  | OP2  | WM1  | WM0  | 91h     |

| 20h  | AWRR | R/W |      |      | X5   | X4   | Х3   | X2   | X1   | X0   | 27h     |

| 21h  | DWRR | R/W |      |      | A5   | A4   | A3   | A2   | A1   | A0   | 27h     |

| 30h  | AWBR | R/W | Y7   | Y6   | Y5   | Y4   | Y3   | Y2   | Y1   | Y0   | EFh     |

| 31h  | DWBR | R/W | В7   | B6   | B5   | B4   | В3   | B2   | B1   | B0   | EFh     |

| 40h  | AWLR | R/W |      |      | SS5  | SS4  | SS3  | SS2  | SS1  | SS0  | 00h     |

| 41h  | DWLR | R/W |      |      | C5   | C4   | C3   | C2   | C1   | C0   | 00h     |

| 50h  | AWTR | R/W | SC7  | SC6  | SC5  | SC4  | SC3  | SC2  | SC1  | SC0  | 00h     |

| 51h  | DWTR | R/W | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   | 00h     |

| 60h  | CPXR | R/W |      |      | RS5  | RS4  | RS3  | RS2  | RS1  | RS0  | 00h     |

| 61h  | BGSG | R/W |      |      | DS5  | DS4  | DS3  | DS2  | DS1  | DS0  | 00h     |

| 70h  | CPYR | R/W | RC7  | RC6  | RC5  | RC4  | RC3  | RC2  | RC1  | RC0  | 00g     |

| 71h  | BGCM | R/W | CB7  | CB6  | CB5  | CB4  | CB3  | CB2  | CB1  | CB0  | 00h     |

| 72h  | EDCM | R/W | CD7  | CD6  | CD5  | CD4  | CD3  | CD2  | CD1  | CD0  | EFh     |

| 80h  | BTMR | R/W | BT7  | BT6  | BT5  | BT4  | BT3  | BT2  | BT1  | BT0  | 33h     |

| 81h  | FRCA | R/W |      |      |      |      |      |      |      |      | 00h     |

| 90h  | SCCR | R/W | CK7  | CK6  | CK5  | CK4  | CK3  | CK2  | CK1  | CK0  | 04h     |

| 91h  | FRCB | R/W |      |      |      |      |      |      |      |      | 00h     |

| A0h  | INTR | R/W | INK  | INT  | INX  | INY  | MSK  | MST  | MSX  | MSY  | 00h     |

| A1h  | KSCR | R/W | KEN  | KSZ  | KDT1 | KDT0 |      | KF2  | KF1  | KF0  | 00h     |

| A2h  | KSDR | RO  | KS7  | KS6  | KS5  | KS4  | KS3  | KS2  | KS1  | KS0  | 00h     |

| A3h  | KSER | RO  | KD7  | KD6  | KD5  | KD4  | KD3  | KD2  | KD1  | KD0  | 00h     |

| B0h  | INTX | R/W |      |      | IX5  | IX4  | IX3  | IX2  | IX1  | IX0  | 27h     |

| B1h  | INTY | R/W | IY7  | IY6  | IY5  | IY4  | IY3  | IY2  | IY1  | IY0  | EFh     |

| C0h  | TPCR | R/W | AZEN | AZOE |      | SCAN | AS3  | AS2  | AS1  | AS0  | 00h     |

| C1h  | TPSR | R/W | ARDY | ADET | 1    | 1    | AF1  | AF0  |      |      | 0Fh     |

| C8h  | TPXR | RO  | TPX9 | TPX8 | TPX7 | TPX6 | TPX5 | TPX4 | TPX3 | TPX2 | 00h     |

| C9h  | TPYR | RO  | TPY9 | TPY8 | TPY7 | TPY6 | TPY5 | TPY4 | TPY3 | TPY2 | 00h     |

| CAh  | TPZR | RO  | TPX1 | TPX0 |      |      | TPY1 | TPY0 |      |      | 00h     |

| D0h  | LCCR | R/W | DZEN |      |      | DAC4 | DAC3 | DAC2 | DAC1 | DAC0 | 8Fh     |

| E0h  | PNTR | R/W | FD7  | FD6  | FD5  | FD4  | FD3  | FD2  | FD1  | FD0  | 00h     |

| F0h  | FNCR | R/W | TNS  | BNK  | RM1  | RM0  | FDA  | ASC  | ABS1 | ABS0 | 92h     |

| F1h  | FVHT | R/W | FH1  | FH0  | FV1  | FV0  | 1    | 1    | 1    | 1    | 0Fh     |

SPEC. REV.02 PAGE 6 OF 24

# REGISTER DESCRIPTION

REG [00h] Whole Chip LCD Controller Register (WLCR)

| Bit | Description                                                                                                                                                                                                                                                                                             | Text/Graph | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|--------|

| 7-6 | Power Mode  1 1: Normal Mode. All of the functions of RA8803/8822 are available in this mode.  0 0: Off Mode. When RA8803/8822 is in off mode, all of functions enter power-off mode, except the wake-up trigger block. If wake-up event occurred, RA8803/8822 would wake-up and return to Normal mode. | 1          | 3h      | R/W    |

| 5   | Software Reset: 1 : Reset all registers except flushing RAM 0 : Normal Operation                                                                                                                                                                                                                        |            | 0h      | R/W    |

| 4   | Reserved.                                                                                                                                                                                                                                                                                               |            | 0h      | R/W    |

| 3   | Display Mode Selection  1 : Character Mode. The written data will be treated as a GB/BIG/ASCII code.  0 : Graphical Mode. The written data will be treated as a bitmap pattern.                                                                                                                         | -1         | 1h      | R/W    |

| 2   | Set Display On/Off Selection  The bit is used to control LCD Driver Interface signals DISP_OFF.  1: DISP_OFF pin output high(Display On).  0: DISP_OFF pin output low(Display Off).                                                                                                                     | Text/Graph | 0h      | R/W    |

| 1   | Blink Mode Selection  1 : Blink Full Screen. The blink time is set by register BTMR.  0 : Normal Display.                                                                                                                                                                                               | Text/Graph | 0h      | R/W    |

| 0   | Inverse Mode Selection  1 : Normal Display  0 : Inverse Full Screen. It will cause the display inversed.                                                                                                                                                                                                | Text/Graph | 1h      | R/W    |

## REG [01h] Misc. Register (MISC)

| Bit | Description                        | Default | Access |

|-----|------------------------------------|---------|--------|

| 7   | Reserved.                          | 1h      | R/W    |

|     | Clock Output (Pin CLK_OUT) Control |         |        |

| 6   | 1 : Enable                         | 1h      | R/W    |

|     | 0 : Disable                        |         |        |

| 5   | Reserved.                          | 1h      | R/W    |

| 4   | Interrupt (INT) and Busy Polarity  | 1h      | R/W    |

| "   | 1 : Set Active High                | ""      | F/VV   |

SPEC. REV.02 PAGE 7 OF 24

|     | 0 : Set Active Low    |    |     |

|-----|-----------------------|----|-----|

| 3-2 | Reserved.             | 0h | R/W |

|     | Clock Speed Selection |    |     |

|     | 0 0 : 3MHz            |    |     |

| 1-0 | 0 1 : 4MHz            | 0h | R/W |

|     | 1 0 : 8MHz            |    |     |

|     | 1 1 : 12MHz           |    |     |

# REG [02h] Advance Power Setup Register (APSR)

| Bit | Description                   | Default | Access |

|-----|-------------------------------|---------|--------|

| 7-6 | Reserved                      | 0h      | R/W    |

| 5-4 | ROM/RAM Reading Speed         |         |        |

|     | 0 0 : Speed0 (30ns@Vdd=3.3V)  |         |        |

|     | 0 1 : Speed1 (60ns@Vdd=3.3V)  | 1h      | R/W    |

|     | 1 0 : Speed2 (90ns@Vdd=3.3V)  |         |        |

|     | 1 1 : Speed3 (120ns@Vdd=3.3V) |         |        |

|     | Font ROM Readable for MPU     |         |        |

| 3   | 1 : Enable                    | 0h      | R/W    |

|     | 0 : Disable                   |         |        |

| 2   | Reserved                      | 0h      | R/W    |

|     | Scrolling Reset for Start     |         |        |

| 1   | 0 : Disable                   | 0h      | R/W    |

|     | 1 : Enable                    |         |        |

| 0   | Reserved                      | 0h      | R/W    |

# REG [03h] Advance Display Setup Register (ADSR)

| Bit | Description                                                       | Default | Access |

|-----|-------------------------------------------------------------------|---------|--------|

| 7-4 | Reserved                                                          | 8h      | R/W    |

|     | Set Display RAM Order (Byte)                                      |         |        |

| 3   | 1 : Inverse Data of Byte                                          | 0h      | R/W    |

|     | 0 : Normal Mode                                                   |         |        |

|     | Common Auto Scrolling                                             |         |        |

| 2   | 1 : Enable                                                        | 0h      | R/W    |

|     | 0 : Disable                                                       |         |        |

|     | Segment Auto Scrolling                                            |         |        |

| 1   | 1 : Enable                                                        | 0h      | R/W    |

|     | 0 : Disable                                                       |         |        |

| 0   | Common or Segment Scrolling Selection                             |         |        |

|     | 1 : Segment Scrolling                                             | 0h      | R/W    |

| l   | 0 : Common Scrolling                                              |         |        |

|     | In Extension Mode(REG[12h] bit[6:4] = "110" "111"), this bit must |         |        |

|     | be high.                                                          |         |        |

SPEC. REV.02 PAGE 8 OF 24

# REG [10h] Whole Chip Cursor Control Register (WCCR)

| Bit | Description                                                                                                                                                                                                          | Text/Graph | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|--------|

| 7   | Auto Increase Cursor Position in Reading DDRAM Operation. 1 : Enable (Auto Increase) 0 : Disable                                                                                                                     | Text/Graph | Oh      | R/W    |

| 6   | Chinese/English Character Alignment  1: Enable  0: Disable  The bit only valid in character mode, that can align full-size and half-size mixed font.                                                                 | Text       | 1h      | R/W    |

| 5   | Store Current Data to DDRAM  1 : Store Current Data to DDRAM Directly  0 : Store Current Data to DDRAM Inversely                                                                                                     | Text/Graph | 1h      | R/W    |

| 4   | Bold Font (Character Mode Only)  1 : Bold Font  0 : Normal Font                                                                                                                                                      | Text       | 0h      | R/W    |

| 3   | Auto Increase Cursor Position in Writing DDRAM Operation.  1 : Enable (Auto Increase) 0 : Disable                                                                                                                    | Text/Graph | 1h      | R/W    |

| 2   | Cursor Display  1 : Set Cursor Display On  0 : Set Cursor Display Off                                                                                                                                                | Text/Graph | 1h      | R/W    |

| 1   | Cursor Blinking 1 : Blink Cursor. The blink time is determined by BTMR. 0 : Normal                                                                                                                                   | Text/Graph | 1h      | R/W    |

| 0   | Cursor Width  1: Cursor width is auto adjust by input data. When half size font, the width is one bit(8 Pixel). When full size font, the width is two bit(16 Pixel).  0: Cursor is fixed at one byte width(8 Pixel). |            | 1h      | R/W    |

# REG [11h] Distance of Words or Lines Register (DWLR)

| Bit | Description       | Default | Access |

|-----|-------------------|---------|--------|

| 7-4 | Set Cursor Height | 2h      | R/W    |

| 3-0 | Set Line Distance | 2h      | R/W    |

SPEC. REV.02 PAGE 9 OF 24

# REG [12h] Memory Access Mode Register (MAMR)

| Bit | Description                                                                               | Default | Access |

|-----|-------------------------------------------------------------------------------------------|---------|--------|

|     | In Graphic Mode, Cursor Auto Shifting Direction                                           |         |        |

| 7   | 1 : Horizontal moving first then Vertical.                                                | 1h      | R/W    |

|     | 0 : Vertical moving first then Horizontal.                                                |         |        |

|     | Display Layer Selection                                                                   |         |        |

|     | 0 0 1 : Only Show Page1                                                                   |         |        |

|     | 0 1 0 : Only Show Page2                                                                   |         |        |

|     | 0 1 1 : Show Two Layer Mode. The display rule depends on Bit3 and                         |         |        |

|     | Bit2 as following.                                                                        |         |        |

|     | 0 0 0 : Gray Mode. In this mode, each pixel gray of LCD depends on                        |         |        |

|     | the value of Page1 & Page2.                                                               |         |        |

|     | Page1 Page2 Gray                                                                          |         |        |

| 6-4 | <br>0 0 Level1                                                                            | 1h      | R/W    |

|     | 1 0 Level2                                                                                |         |        |

|     | 0 1 Level3                                                                                |         |        |

|     | 1 1 Level4                                                                                |         |        |

|     | 1.1.0 : Extension Mode(1), the nanel will show both Dage1 and                             |         |        |

|     | 1 1 0 : Extension Mode(1), the panel will show both Page1 and                             |         |        |

|     | Page2. The RA8803 is available for 640x240 dots panel, and RA8822 for 480x160 dots panel. |         |        |

|     | 1 1 1 : Extension Mode(2), the panel will show both Page1 and                             |         |        |

|     | Page2. The RA8803 is available for 320x480 dots panel, and                                |         |        |

|     | RA8822 for 240x320 dots panel.                                                            |         |        |

|     | Two Layer Mode Selection                                                                  |         |        |

|     | 0 0 : Page1 RAM "OR" Page2 RAM                                                            |         |        |

| 0.0 | 0 1 : Page1 RAM "XOR" Page2 RAM                                                           | O.L.    | D.044  |

| 3-2 | 1 0 : Page1 RAM "NOR" Page2 RAM                                                           | 0h      | R/W    |

|     | 1 1 : Page1 RAM "AND" Page2 RAM                                                           |         |        |

|     | Please refer to Figure 7-10 for more explanation.                                         |         |        |

|     | MPU Read/Write Layer Selection                                                            |         |        |

|     | 0 0 : Access Page0 (512B SRAM) Display Data RAM.                                          |         |        |

|     | 0 1 : Access Page1 (9.6KB SRAM) Display Data RAM.                                         |         |        |

| 1-0 | 1 0 : Access Page2 (9.6KB SRAM) Display Data RAM.                                         | 1h      | R/W    |

|     | 1 1 : Access Page1 and Page2 Display Data RAM at the same time.                           |         |        |

|     | The Page0 are used for create some temporary characters. Please                           |         |        |

|     | refer to AP Note for more details.                                                        |         |        |

SPEC. REV.02 PAGE 10 OF 24

#### REG [20h] Active Window Right Register (AWRR)

| Bit | Description                                  | Default | Access |

|-----|----------------------------------------------|---------|--------|

| 7-6 | Reserved                                     | 0h      | R      |

| 5-0 | Active Window Right Position → Segment-Right | 27h     | R/W    |

**Note:** REG [20h, 30h, 40h, 50h] are used for the function of change the line and page. Users can use these four Registers to set a block as an active window. When data goes beyond the right boundary of active window (The value is set by REG [20h, 30h, 40h, 50h]), then the cursor will automatically change the line and write in data continuously. It means the cursor will move to the left boundary of active window, which is set by REG [40h]. When the data comes to the bottom line of the right side (set by REG [20h and 30h]), then the cursor will be moved to the first line of the left side automatically and continue to put in data. (set by REG [40h, 50h]).

#### REG [30h] Active Window Bottom Register (AWBR)

| Bit | Description                                   | Default | Access |

|-----|-----------------------------------------------|---------|--------|

| 7-0 | Active Window Bottom Position → Common-Bottom | EFh     | R/W    |

#### REG [40h] Active Window Left Register (AWLR)

| Bit | Description                                | Default | Access |

|-----|--------------------------------------------|---------|--------|

| 7-6 | Reserved                                   | 0h      | R      |

| 5-0 | Active Window Left Position → Segment-Left | 0h      | R/W    |

### REG [50h] Active Window Top Register (AWTR)

| Bit | Description                             | Default | Access |

|-----|-----------------------------------------|---------|--------|

| 7-0 | Active Window Top Position → Common-Top | 0h      | R/W    |

#### REG [21h] Display Window Right Register (DWRR)

| Bit | Description                                                                                                                                                                                                    | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                                                                                                                                                                       | 0h      | R/W    |

|     | Set Display Window Right Position → Segment-Right                                                                                                                                                              |         |        |

|     | Segment-Right = (Segment Number / 8) – 1                                                                                                                                                                       |         |        |

| 5-0 | RA8803: If LCD panel resolution is $320*240$ , the value of the register is: $(320/8) - 1 = 39 = 27h$<br>RA8822: If LCD panel resolution is $240*160$ , the value of the register is: $(240/8) - 1 = 29 = 1Dh$ | 27h     | R/W    |

**Note:** REG[21h, 31h, 41h, 51h] are used to set Display Window Resolution. Users can set the viewing scope of Display RAM. Column Address of RA8803 can be set between 0~27h, and Row Address can be set between 0~EFh. Column Address of RA8822 can be set between 0~1Dh, and Row Address can be set between 0~9Fh. Users can set start and end address first, and then by adding shift function to present the effect of rolling.

SPEC. REV.02 PAGE 11 OF 24

### REG [31] Display Window Bottom Register (DWBR)

| Bit | Description                                                                                              | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------|---------|--------|

|     | <b>Display Window Bottom Position</b> → Common-Bottom                                                    |         |        |

|     | Common_ Bottom = LCD Common Number –1 + n                                                                |         |        |

| 7-0 | RA8803: If LCD panel resolution is $320*240(n=0)$ , the value of the register is: $240 - 1 = 239 = EFh$  | EFh     | R/W    |

|     | RA8822: If LCD panel resolution is $240*160(n=0)$ , the value of the register is: $160 - 1 = 159 = 9$ Fh |         |        |

|     |                                                                                                          |         |        |

### REG [41] Display Window Left Register (DWLR)

| Bit | Description                                 | Default | Access |

|-----|---------------------------------------------|---------|--------|

| 7-0 | Display Window Left Position → Segment-Left | 0h      | R/W    |

| 7-0 | Usually set "0h".                           | OII     | 17/00  |

### REG [51] Display Window Top Register (DWTR)

|   | Bit | Description                                     | Default | Access |

|---|-----|-------------------------------------------------|---------|--------|

|   | 7-0 | <b>Display Window Top Position</b> → Common-Top | 0h R    | R/W    |

| L | 7-0 | Usually set "0h".                               | OH      | 1000   |

Note: For some registers setting, please refer the following rule:

- 1. DWRR≥ AWRR≥ CPXR≥ AWLR≥ DWLR

- 2.  $DWBR \ge AWBR \ge CPYR \ge AWTR \ge DWTR$

### REG [60h] Cursor Position X Register (CPXR)

| Bit | Description                | Default | Access |

|-----|----------------------------|---------|--------|

| 7-6 | Reserved                   | 0h      | R      |

| 5-0 | Cursor Position of Segment | 0h      | R/W    |

### REG [61h] Begin Segment Position Register (BGSG)

| Bit | Description                              | Default | Access |

|-----|------------------------------------------|---------|--------|

| 7-6 | Reserved                                 | 0h      | R/W    |

| 5-0 | Segment Start Position of Scrolling Mode | 0h      | R/W    |

### REG [70h] Cursor Position Y Register (CPYR)

| Bit | Description               | Default | Access |

|-----|---------------------------|---------|--------|

| 7-0 | Cursor Position of Common | 0h      | R/W    |

SPEC. REV.02 PAGE 12 OF 24

### REG [71h] Scrolling Action Range, Begin Common Register (BGCM)

|   | Bit | Description                             | Default | Access |

|---|-----|-----------------------------------------|---------|--------|

| ſ | 7-0 | Common Start Position of Scrolling Mode | 0h      | R/W    |

# REG [72h] Scrolling Action Range END Common Register (EDCM)

|   | Bit | Description                              | Default | Access |

|---|-----|------------------------------------------|---------|--------|

| ſ | 7-0 | Common Ending Position of Scrolling Mode | EFh     | R/W    |

### REG [80h] Blink Time Register (BTMR)

| Bit | Description                                          | Default | Access |

|-----|------------------------------------------------------|---------|--------|

|     | Cursor Blink Time                                    |         |        |

| 7-0 | Blinking Time = Bit [70] x (1/Frame_Rate)            | 33h     | R/W    |

|     | The setup of Frame Rate is depends on the LCD panel. |         |        |

### REG [81h] Frame Rate Polarity Change at Common\_A Register (FRCA)

| Bi | it | Description | Default | Access |

|----|----|-------------|---------|--------|

| 7- | 0  | Reserved    | 0h      | R/W    |

### REG [91h] Frame Rate Polarity Change at Common\_B Register (FRCB)

| Bit | Description | Default | Access |

|-----|-------------|---------|--------|

| 7-0 | Reserved    | 0h      | R/W    |

### REG [90h] Shift Clock Control Register (SCCR)

| Bit | Description                                                         | Default | Access |

|-----|---------------------------------------------------------------------|---------|--------|

|     | Shift Clock Cycle                                                   |         |        |

|     | SCCR = (SCLK x DW) / (Seg x Com x FRM)                              |         |        |

|     | SCLK: RA8803/8822 System Clock (Unit: Hz)                           | 4h      | R/W    |

|     | DW : Bus Width of LCD Driver(Unit : Bit)                            |         |        |

| 7-0 | Seg : Segment Number of LCD Panel(Unit : Pixel)                     |         |        |

|     | Com : Common Number of LCD Panel (Unit : Pixel)                     |         |        |

|     | FRM : Frame Rate of LCD Panel(Unit : Hz)                            |         |        |

|     | <b>Note:</b> SYS_DW=0, If LCD Data Bus is 4it then SCCR has to ≥ 4. |         |        |

|     | SYS_DW=1, If LCD Data Bus is 8it then SCCR has to $\geq$ 2.         |         |        |

SPEC. REV.02 PAGE 13 OF 24

# REG [A0h] Interrupt Setup & Status Register (INTR)

| Bit | Description                                                                                                                                              | Default | Access               |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|

| 7   | Key Scan Interrupt Flag  1 : Key Scan Detects Key Input  0 : Key Scan doesn't Detect Key Input                                                           | 0h      | R<br>(Read<br>Clear) |

| 6   | Touch Panel Detect  1 : Touch Panel Touched  0 : Touch Panel Untouched                                                                                   | 0h      | R<br>(Read<br>Clear) |

| 5   | Cursor Column Status  1 : The Cursor Column is equal to INTX  0 : The Cursor Column is not equal to INTX                                                 | 0h      | R<br>(Read<br>Clear) |

| 4   | Cursor Row Status  1 : The Cursor Row is equal to INTY  0 : The Cursor Row is not equal to INTY                                                          | 0h      | R<br>(Read<br>Clear) |

| 3   | Key Scan Interrupt Mask  1 : Enable Key Scan Interrupt  0 : Disable Key Scan Interrupt                                                                   | 0h      | R/W                  |

| 2   | Touch Panel Interrupt Mask  1 : Generate interrupt output if touch panel was detected.  0 : Don't generate interrupt output if touch panel was detected. | 0h      | R/W                  |

| 1   | Register[B0h] INTX Event Mask  1 : Enable INTX Interrupt  0 : Disable INTX Interrupt                                                                     | 0h      | R/W                  |

| 0   | Register[B1h] INTY Event Mask  1 : Enable INTY Interrupt  0 : Disable INTY Interrupt                                                                     | 0h      | R/W                  |

# REG [A1h] Key Scan Controller Register (KSCR)

| Bit | Description                  | Default | Access |

|-----|------------------------------|---------|--------|

|     | Key Scan Enable Bit          |         |        |

| 7   | 1 : Enable                   | 0h      | R/W    |

|     | 0 : Disable                  |         |        |

|     | Key Scan Matrix Selection    |         |        |

| 6   | 1 : 4x4 Matrix               | 0h      | R/W    |

|     | 0 : 8x8 Matrix               |         |        |

|     | Key Scan Data Sampling Times |         |        |

|     | 0 0 : 2h                     |         |        |

| 5-4 | 0 1 : 4h                     | 0h      | R/W    |

|     | 1 0 : 8h                     |         |        |

|     | 1 1 : 16h                    |         |        |

| 3   | Reserved                     | 0h      | R/W    |

| 2-0 | Key Scan Frequency Selection | 0h      | R/W    |

SPEC. REV.02 PAGE 14 OF 24

| 0 0 0 : 2 x FRM   |  |

|-------------------|--|

| 0 0 1 : 4 x FRM   |  |

| 0 1 0 : 8 x FRM   |  |

| 0 1 1 : 16 x FRM  |  |

| 1 0 0 : 32 x FRM  |  |

| 1 0 1 : 64 x FRM  |  |

| 1 1 0 : 128 x FRM |  |

| 1 1 1 : 256 x FRM |  |

### REG [A2h] Key Scan Data Register (KSDR)

| Bit | Description             | Default | Access |

|-----|-------------------------|---------|--------|

| 7-0 | Key Scan KC[7~0] Output | 0h      | R      |

### REG [A3h] Key Scan Data Expand Register (KSER)

| Bit | Description            | Default | Access |

|-----|------------------------|---------|--------|

| 7-0 | Key Scan KR[7~0] Input | 0h      | R      |

### REG [B0h] Interrupt Column Setup Register (INTX)

| Bit | Description                                                  | Default | Access |

|-----|--------------------------------------------------------------|---------|--------|

| 7-6 | Reserved                                                     | 0h      | R      |

|     | Column Address of Interrupt                                  |         |        |

| 5-0 | If Cursor Position X Register (CPXR)=INTX, then an interrupt | 27h     | R/W    |

|     | occurred.                                                    |         |        |

### REG [B1h] Interrupt Row Setup Register (INTY)

| Bit | Description                                                                                          | Default | Access |

|-----|------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Row Address of Interrupt  If Cursor Position Y Register (CPYR)=INTY, then an interrupt has occurred. | EFh     | R/W    |

SPEC. REV.02 PAGE 15 OF 24

# REG [D0h] LCD Contrast Control Register (LCCR)

| Bit | Description               | Default | Access |

|-----|---------------------------|---------|--------|

|     | DAC Function              |         |        |

| 7   | 1 : Disable               | 1h      | R/W    |

|     | 0 : Enable                |         |        |

| 6-5 | Reserved                  | 0h      |        |

|     | DAC Driving Current       |         |        |

|     | 0 0 0 0 b (Min. Current)  |         |        |

| 4-0 | :                         | 0Fh     | R/W    |

| 4-0 | :                         | OFII    | TV VV  |

|     | :                         |         |        |

|     | 1 1 1 1 1b (Max. Current) |         |        |

# REG [E0h] Pattern Data Register (PNTR)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | <ul> <li>(1) Data Written to DDRAM</li> <li>When REG[F0h] bit3 is '1', it will read the data from Register [E0h] and fill the whole DDRAM. After the movement of filling the Active window, REG [F0h] bit3 will become "0".</li> <li>(2) Display Times of Gray Mode</li> <li>For Gray Mode(Register MAMR bit[64] = 000), These register used to control the display times. If the frame rate is fixed, the number of "1" and "0" are represent the display ratio of 1 and 0. Please see Chapter 7-10 and AP Note 9-23 for more description.</li> </ul> | 0h      | R/W    |

# REG [F0h] Font Control Register (FNCR)

| Bit | Description                                            | Text/Graph | Default | Access |

|-----|--------------------------------------------------------|------------|---------|--------|

|     | Font ROM Transfer Circuit                              |            |         |        |

| 7   | 1 : Enable                                             |            | 1h      | R/W    |

|     | 0 : Bypass                                             |            |         |        |

|     | When bit5~4 set as "00" → ROM Mode0, this bit could be |            |         |        |

| 6   | used to select the upper or lower part of 256KB ROM.   |            | 0h      | R/W    |

| O   | 1 : Select lower part of 256KB ROM                     |            |         | 13/11  |

|     | 0 : Select upper part of 256KB ROM                     |            |         |        |

|     | Select Font ROM Type                                   |            |         |        |

| 5-4 | 0 0 : Select GB font ROM (256KB, Mode0)                |            | 1h      | R/W    |

| 5-4 | 0 1 : Select BIG5 font ROM (512KB, Mode1)              |            |         | IX/VV  |

|     | 1 0 : Support GB font ROM (512KB, Mode2)               |            |         |        |

|     | Fill PNTR Data to DDRAM                                |            |         |        |

| 3   | 1 : Fill Data to DDRAM Enable                          | Graph      | 0h      | R/W    |

|     | 0 : No Action                                          |            |         |        |

SPEC. REV.02 PAGE 16 OF 24

CV240160C

|     | When this bit is "1", RA8803/8822 will automatically read PNTR data, and fill it to DDRAM (Range:[AWLR, AWTR] ~ [AWRR, AWBR]), and then this bit will be cleaned to "0".                                                                                            |      |    |                     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|---------------------|

| 2   | ASCII Code Selection  1 : All input data will be decoded as ASCII (00~FFh)  0 : The RA8803/8822 will check the first byte data first. If the first byte is 00~9Fh then regarded as ASCII (Half-size). If first byte is A0~FFh then regarded as GB/BIG5 (Full-size). | Text | 0h | R/W<br>(Auto Clear) |

| 1-0 | ASCII Blocks Select  0 0 : Map to ASCII block 0, Latin_1  0 1 : Map to ASCII block 1, Latin_2  1 0 : Map to ASCII block 2, Latin_3  1 1 : Map to ASCII block 3, Latin_4                                                                                             | 1    | 2h | R/W                 |

# REG [F1h] Font Size Control Register (FVHT)

| Bit | Description                 | Default | Access |

|-----|-----------------------------|---------|--------|

|     | Set Character Horizon Size  |         |        |

|     | 0 0 : One Time              |         |        |

| 7-6 | 0 1 : Two Times             | 0h      | R/W    |

|     | 1 0 : Three Times           |         |        |

|     | 11: Four Times              |         |        |

|     | Set Character Vertical Size |         |        |

|     | 0 0 : One Time              |         |        |

| 5-4 | 0 1 : Two Times             | 0h      | R/W    |

|     | 10: Three Times             |         |        |

|     | 11: Four Times              |         |        |

| 3-0 | Reserved                    | Fh      | R/W    |

SPEC. REV.02 PAGE 17 OF 24

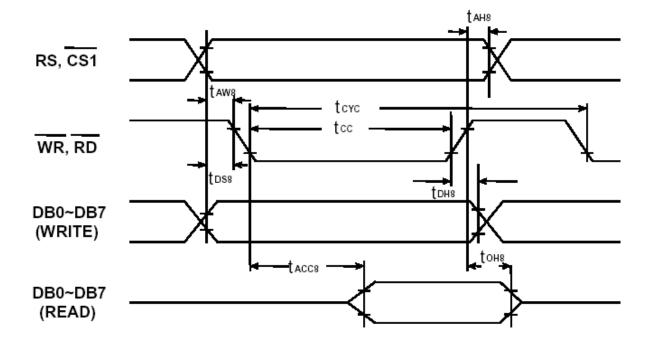

# A.C. CHARACTERISTICS

# 1. For 8080 series :

| Signal      | Symbol            | bol Parameter Rating |     | Unit | Condition |                       |

|-------------|-------------------|----------------------|-----|------|-----------|-----------------------|

| Olgilai     | Oyillooi          | i di dilletei        | Min | Max  | Oill      | Condition             |

| RS, CS1#    | t <sub>AH8</sub>  | Address hold time    | 10  | -    | ns        | System Clock:         |

| K3, C31#    | t <sub>Aw8</sub>  | Address setup time   | 63  | ŀ    | ns        | 8MHz<br>Voltage: 3.3V |

| WR#, RD#    | t <sub>CYC</sub>  | System cycle time    | 800 |      | ns        | voltage. 5.5 v        |

| VII\π, I\Dπ | t <sub>cc</sub>   | Strobe pulse width   | 400 | 1    | ns        |                       |

|             | t <sub>DS8</sub>  | Data setup time      | 63  | -    | ns        |                       |

| DB0 to DB7  | t <sub>DH8</sub>  | Data hold time       | 10  |      | ns        |                       |

| DB0 10 DB7  | t <sub>ACC8</sub> | RD access time       | 1   | 330  | ns        |                       |

|             | t <sub>OH8</sub>  | Output disable time  | 10  | ı    | ns        |                       |

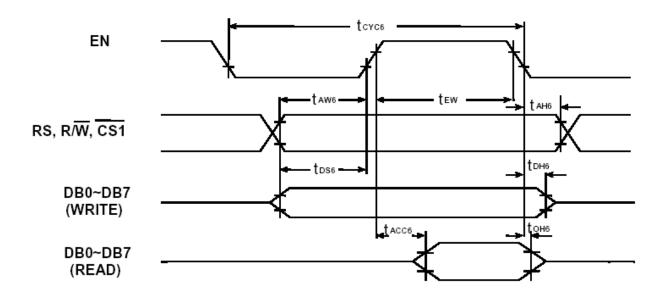

# 2. For 6800 series :

| Signal            | Symbol            | Parameter           | Rating |     | Rating | Unit                  | Condition |

|-------------------|-------------------|---------------------|--------|-----|--------|-----------------------|-----------|

| Signal            | Syllibol          | raiailletei         | Min    | Max | Oilit  | Condition             |           |

|                   | t <sub>AH6</sub>  | Address hold time   | 10     | 1   | ns     | System Clock:<br>8MHz |           |

| A0, R/W#,<br>CS1# | t <sub>Aw6</sub>  | Address setup time  | 63     | 1   | ns     | Voltage: 3.3V         |           |

|                   | t <sub>CYC6</sub> | System cycle time   | 800    | 1   | ns     |                       |           |

|                   | t <sub>DS6</sub>  | Data setup time     | 63     | 1   | ns     |                       |           |

| DB0 to DB7        | t <sub>DH6</sub>  | Data hold time      | 10     | 1   | ns     |                       |           |

| DB0 t0 DB7        | t <sub>ACC6</sub> | Access time         | 1      | 330 | ns     |                       |           |

|                   | t <sub>OH6</sub>  | Output disable time | 10     | -   | ns     |                       |           |

| EN                | $t_{\text{EW}}$   | Enable pulse width  | 400    |     | ns     |                       |           |

SPEC. REV.02 PAGE 18 OF 24

### TIMING DIAGRAMS

### 1. For 8080 series :

### 2. For 6800 series :

SPEC. REV.02 PAGE 19 OF 24

#### **DATA ACCESS WITH MCU**

| No. | RS | 6800 | 0808 |     | DB0-DB7                | Function                                                                                                                                 |

|-----|----|------|------|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|     |    | R/W# | RD#  | WR# | מם-מם                  | Function                                                                                                                                 |

| 1   | 1  | 1    | 0    | 1   | xxh                    | Read Display Data                                                                                                                        |

| 2   | 1  | 0    | 1    | 0   | High Byte<br>>Low Byte | Write Display Data (Character Mode – Chinese): Execute Step ② twice. At first, write the High Byte of Chinese Code, then write Low Byte. |

| 3   | 1  | 0    | 1    | 0   | xxh                    | Write Display Data (Character Mode –<br>English, ASCII)                                                                                  |

| 4   | 1  | 0    | 1    | 0   | xxh                    | Write Display Data (Graphic Mode)                                                                                                        |

| (5) | 0  | 0    | 1    | 0   | Address                | Read Data(Status) from Register: Step ⑤ → Step ⑥                                                                                         |

| 6   | 0  | 1    | 0    | 1   | Status                 |                                                                                                                                          |

| 7   | 0  | 0    | 1    | 0   | Address                | Write Command to Register: Step ⑦ → Step ®                                                                                               |

| 8   | 0  | 0    | 1    | 0   | Command                |                                                                                                                                          |

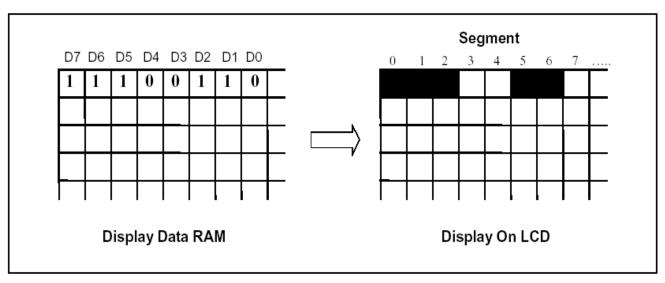

#### **DISPLAY DATA RAM**

The RA8822 support 240Column x 160Row for maximum panel, so it need 4.8Kbyte display RAM. If some place in DDRAM was filled in "1", then the corresponding place of LCD panel will be lighted up. Please see below:

SPEC. REV.02 PAGE 20 OF 24

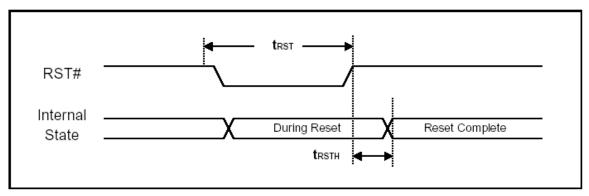

#### **RESET TIMING**

Reset timing: trst must over 250ms and trsth must over 50ms. The RA8822 Reset need enough time to complete the reset procedure.

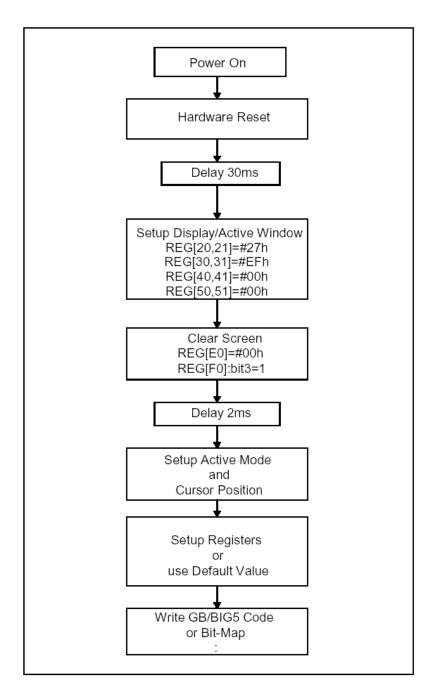

#### RESET PROCESS

SPEC. REV.02 PAGE 21 OF 24

### **ELECTRO-OPTICAL CHARACTERISTICS**

MEASURING CONDITION: POWER SUPPLY = Vop / 64 Hz

TEMPERATURE =  $23 \pm 5$  °C

RELATIVE HUMIDITY =  $60 \pm 20 \%$

| ITEM           | SYMBOL | UNIT | TYP. STN |

|----------------|--------|------|----------|

| DESDONISE TIME | Ton    | ms   | 320      |

| RESPONSE TIME  | Toff   | ms   | 430      |

| CONTRAST RATIO | Cr     | -    | 8        |

|                | V3:00  | 0    | 40       |

| VIEWING ANGLE  | V6:00  | 0    | 55       |

| (Cr ≥ 2)       | V9:00  | 0    | 40       |

|                | V12:00 | 0    | 35       |

THE ELECTRO-OPTICAL CHARACTERISTICS ARE MEASURED VALUE BUT NOT GUARANTEED ONES.

SPEC. REV.02 PAGE 22 OF 24

## RELIABILITY OF LCD MODULE

|                              | •                             |                               |           |  |

|------------------------------|-------------------------------|-------------------------------|-----------|--|

|                              | TEST CONDITION                | TEST CONDITION                |           |  |

| ITEM                         | FOR NORMAL TEMPERATURE        | FOR WIDE TEMPERATURE          | TIME      |  |

| High temperature operating   | 50°C                          | 70°C                          | 240 hours |  |

| Low temperature operating    | 0°C                           | -20°C                         | 240 hours |  |

| High temperature storage     | 60°C                          | 80°C                          | 240 hours |  |

| Low temperature storage      | -10°C                         | -30°C                         | 240 hours |  |

| Temperature-humidity storage | 40°C 90% R.H.                 | 60°C 90% R.H.                 | 96 hours  |  |

| Temperature cycling          | -10°C to 60°C -30°C to 80°C   |                               | 5 avala   |  |

|                              | 30 Min Dwell                  | 30 Min Dwell                  | 5 cycle   |  |

| Vibration Test at LCM Level  | Freq 10-55 Hz                 | Freq 10-55 Hz                 |           |  |

|                              | Sweep rate: 10-55-10 at 1 min | Sweep rate: 10-55-10 at 1 min |           |  |

|                              | Sweep mode Linear             | Sweep mode Linear             | _         |  |

|                              | Displacement: 2 mm p-p        | Displacement: 2 mm p-p        |           |  |

|                              | 1 Hour each for X, Y, Z       | 1 Hour each for X, Y, Z       |           |  |

# QUALITY STANDARD OF LCD MODULE

| 1.0 | Sampling Method                         |                 |                                     |  |  |  |  |  |

|-----|-----------------------------------------|-----------------|-------------------------------------|--|--|--|--|--|

|     | Sampling Plan: MIL                      | STD 105 E       |                                     |  |  |  |  |  |

|     | Class of AQL : Level II/Single Sampling |                 |                                     |  |  |  |  |  |

|     | Critical: 0.25% Major 0.65% Minor 1.5%  |                 |                                     |  |  |  |  |  |

| 2.0 | Defect Group Failure Categor            |                 | Failure Reasons                     |  |  |  |  |  |

|     | Critical Defect                         | Malfunction     | Open                                |  |  |  |  |  |

|     | 0.25%(AQL)                              |                 | Short                               |  |  |  |  |  |

|     |                                         |                 | Burnt or dead component             |  |  |  |  |  |

|     |                                         |                 | Missing part/improper part P.C.B.   |  |  |  |  |  |

|     |                                         |                 | Broken                              |  |  |  |  |  |

|     | Major Defect                            | Poor Insulation | Potential short                     |  |  |  |  |  |

|     | 0.65%(AQL)                              |                 | High current                        |  |  |  |  |  |

|     |                                         |                 | Component damage or scratched       |  |  |  |  |  |

|     |                                         |                 | or Lying too close improper coating |  |  |  |  |  |

|     |                                         | Poor Conduction | Damage joint                        |  |  |  |  |  |

|     |                                         |                 | Wrong polarity                      |  |  |  |  |  |

|     |                                         |                 | Wrong spec. part                    |  |  |  |  |  |

|     |                                         |                 | Uneven/intermittent contact         |  |  |  |  |  |

|     |                                         |                 | Loose part                          |  |  |  |  |  |

|     |                                         |                 | Copper peeling                      |  |  |  |  |  |

|     |                                         |                 | Rust or corrosion or dirt's         |  |  |  |  |  |

|     | Minor Defect Cosmetic Defect            |                 | Minor scratch                       |  |  |  |  |  |

|     | 1.5%(AQL)                               |                 | Flux residue                        |  |  |  |  |  |

|     |                                         |                 | Thin solder                         |  |  |  |  |  |

|     |                                         |                 | Poor plating                        |  |  |  |  |  |

|     |                                         |                 | Poor marking                        |  |  |  |  |  |

|     |                                         |                 | Crack solder                        |  |  |  |  |  |

|     |                                         |                 | Poor bending                        |  |  |  |  |  |

|     |                                         |                 | Poor packing                        |  |  |  |  |  |

|     |                                         |                 | Wrong size                          |  |  |  |  |  |

SPEC. REV.02 PAGE 23 OF 24

#### HANDLING PRECAUTIONS

### (1) CAUTION OF LCD HANDLING & CLEANING

The polarizing plate on the surface of the panel is made from organic substances. Be very careful for chemicals not to touch the plate or it leads the polarizing plate to deteriorate.

If the use of a chemical is unavoidable, wipe the panel lightly with soft materials, such as gauze and absorbent cotton, soaked in a solvent.

Avoid wiping with a dry cloth, since it could damage the surface of the polarizing plate and others.

Do not expose to direct sunlight or fluorescent light for a long time

#### (2) CAUTION AGAINST STATIC CHARGE

The LCD modules use CMOS LSI drivers, so customers are recommended that any unused input terminal would be connected to  $V_{DD}$  or  $V_{SS}$ , do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity.

#### (3) ESD PRECAUTION

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is recommended to take normal precautions appropriate to handling LCM module. For example: product surface grounding. Always take ESD precaution when handling the *LCD Module*. Components are exposed for direct finger touches and can be damaged unless ESD precaution is taken.

#### (4) PACKAGING

Avoid intense shock and falls from a height and do not operate or store them exposed to direct sunshine or high temperature/humidity for long periods.

#### (5) CAUTION FOR OPERATION

The viewing angle can be adjusted by varying the LCD driving voltage VO.

Driving voltage should be kept within specified range, excess voltage shortens display life.

Response time increases with decrease in temperature.

Display may turn black or dark Blue at temperature above its operational range; this is however not destructive and the display will return to normal once the temperature falls back to range.

Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured". They will recover once the display is turned off.

Condensation at terminals will cause malfunction and possible electrochemical reaction. Relative humidity of the environment should therefore be kept below 60%.

#### (6) SAFETY

Liquid crystal may leak out of a damaged LCD, it is recommended to wash off the liquid crystal by using solvents such as acetone or ethanol and should be burned up later.

If any liquid leak out of a damaged glass cell comes in contact with your hands, wash it off with soap and water immediately.

#### WARRANTY

CLOVER will replace or repair any of her LCD module in accordance with her LCD specification for a period of one year from date of shipment. The warranty liability of Clover is limited to repair and/or replacement. Clover will not be responsible for any subsequent or consequential event.

SPEC. REV.02 PAGE 24 OF 24

<sup>\*</sup>Usable solvent: Alcohol (ethanol, IPA and the like)

<sup>\*</sup>Appropriate solvent: Ketones, ethyl alcohol